01 | CPU缓存:怎样写代码能够让CPU执行得更快?

讲述:陶辉

时长13:48大小11.07M

CPU 的多级缓存

提升数据缓存的命中率

提升指令缓存的命中率

提升多核 CPU 下的缓存命中率

小结

思考题

1716143665 拼课微信(31)

- 2020-04-27因为在多核CPU时代,CPU有“缓存一致性”原则,也就是说每个处理器(核)都会通过嗅探在总线上传播的数据来检查自己的缓存值是不是过期了。如果过期了,则失效。比如声明volitate,当变量被修改,则会立即要求写入系统内存。展开

作者回复: 讲得非常好!忆水寒同学对底层知识理解地很透彻!

14 - 2020-04-27一片连续的内存被加载到不同cpu核心中(就是同一个cache line在不同的cpu核心),其中一个cpu核心中修改cache line,其它核心都失效,加锁也是加在cache line上,其它核心线程也被锁住,降低了性能。解决办法是填充无用字节数,使分开展开

作者回复: 完全正确!二星球同学用过填充法写代码么?或者看到过这样的开源代码?

3 7 - 2020-04-27思考题:

数据从内存加载到高速缓存中,以块为基本单元(一个块64字节),相邻的两个变量很可能在同一块中,当这个数据块分别加载到两颗cpu的高速缓存中时,只要一个cpu对该块(高速缓存中缓存的块)进行写操作,那么另一cpu缓存的该块将失效。

可以通过将两个变量放到不同的缓存块中,来解决这个问题展开 3 5 - 2020-04-27第一篇就进入知识盲区了展开

作者回复: 你好海罗,这门课虽然只有30讲,但会涵盖绝大部分性能优化点,所以每篇文章都会涉及不同的知识。这一篇我希望你能明白CPU缓存的用途,这是成为高手必须了解的知识。

比如,我在protobuf那一讲中,还会讲到protobuf是怎么利用缓存的。所以,你可以先有这么一个概念,在后续用到的时候,再回过头来看,就更容易理解了。 4 - 2020-04-28此时内存是跳跃访问的,如果 N 的数值很大,那么操作 array[j][i]时,是没有办法把 array[j][i+1]也读入缓存的。

---------------------------------------------------------------------------------------------

老师是不是写错了,应该是”那么操作 array[j][i]时,是没有办法把 array[j+1][i](而不是array[j][i+1])也读入缓存的。”展开作者回复: 你好赖阿甘,你读得很仔细,完全正确,我笔误啦,非常感谢你的提醒,稍候我会联系编辑小姐姐更正的。

1 3 - 2020-04-27这个文章其实讲解的很细致,来龙去脉都说清楚了。不错!

其实每篇文章能讲到这个地步,作为读者(也可以称为学生)每篇能够学到一个哪怕很小的知识点,那也是值得的。展开作者回复: 最初这篇文章有6千字,想在一篇文章中讲清楚CPU缓存太难啦,后来编辑小姐姐协助我一点点删下来,还是担心读者看不懂,找不到重点。

忆水寒同学的知识很扎实,你点赞我就放心啦^_^。 1 2 - 2020-04-27陶老师我们集群有一个问题,某一台物理机的CPU会被Hadoop yarn的查询任务打满,并且占用最多的pid在不停的变化,我查看了TIME_WAIT的个数好像也不是很多,在顶峰的时候还没达到一万,能够持续一两个小时。这个问题您有没有什么思路呢?展开

作者回复: 解决性能问题,一般有两种方法:经验派和“理论”派,前者就是基于自己的经验概率,将能想到的优化方法都试一遍,这种方式通常又有效又快速,但无法解决复杂的问题。

所谓理论派,就是沿着固定的思路,使用二分法,从高至低慢慢下沉到细节。具体到你的问题,我建议你先看看,CPU占用是用户态还是系统态,用户态的话就要分析代码了,系统态还要进一步分析。火焰图通常是个很好的办法,虽然搭能画火焰图的环境很麻烦,但这种底层方法很有效的。 2 2 - 2020-04-28对比开篇树图,numa架构貌似还没说,后续会提到吗?

作者回复: 你好Oliver,第1讲的初稿是有提的,但因为numa架构其实是讲访问非本地主存时,性能的降低问题,所以与CPU缓存关系不太直接,后面删除了。本来后面也不会再提到,不过中间有个10道面试题,我跟编辑商量下能不能放在那里提下。

1 - 2020-04-28思考题猜测是False sharing导致的,非常热的数据最好cache line对齐。

作者回复: 是的,好吃不贵的答案更加简洁!

1 - 2020-04-28https://zxs.io/s/o 我之前写过一篇博客详细介绍了cpu分支预测和性能差异,有兴趣可以参考下。

作者回复: 谢谢分享!

1 - 2020-04-27前几天学习了一下计算机组成原理。大部分都能听懂,开心~~~

本节讲到的性能优化实际上是涉及到了计算机组成原理中的【内存的局部性原理】以及【cpu的分支预测】。

对于课后的问题,因为多线程操作某些共享变量,涉及到变量的有效性问题(是否过期),如果变量在一个线程被修改,其他核心中的缓存失效啦。其他线程调用该变量的时候会从内存中重新加载到缓存。

所谓的如何解决,应该是解决缓存失效和保持数据一致性的问题,应该满足两点:

1. 写传播,即通知其他核心,某个缓存失效,需要从内存读取一下

2. 保证事务串行化,事务请求的顺序不能变化

我看资料了解到解决方案是基于总线嗅探机制的MESI协议来解决数据一致性问题。

在Java中,volatile 会确保我们对于这个变量的读取和写入,都一定会同步到主内存里,而不是从 Cache 里面读取,保证了数据一致性问题。

这是我最近学习计算机组成原理后见解,不知道自己理解的有没有问题。有问题希望陶辉老师指正一下。展开作者回复: 你好ByiProX,能够从留言中感受到你最近的进步,非常棒! 你的理解都是正确的,关于思考题你可以看下二星球的留言,他说得很清楚^_^

1 1 - 2020-04-27老师代码准备的真多!

思考题有同学已经回答的非常准确了。

虽然已经看过了 linux性能优化 计算机组成原理 和 性能工程高手课 ,但看起老师的文章还是很有意思。

一些知识也加深了印象。

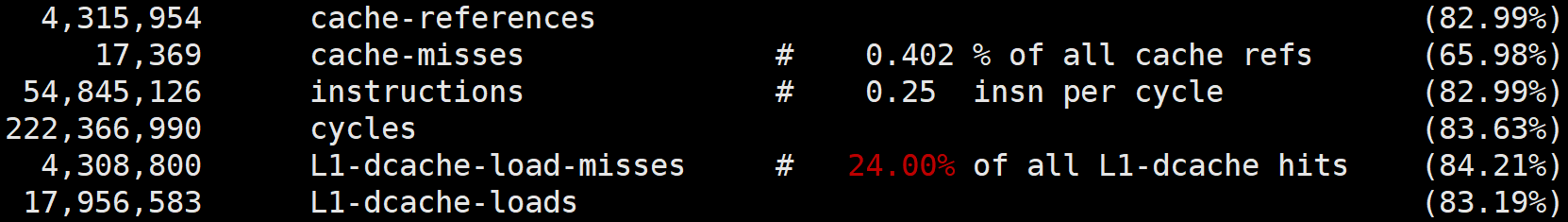

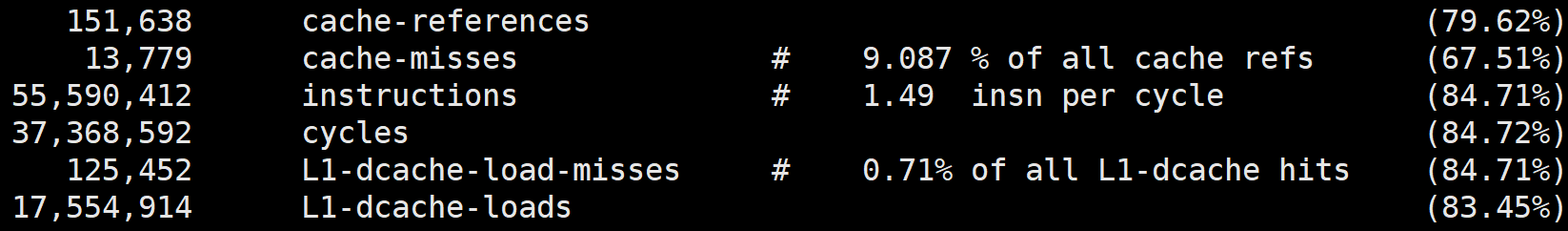

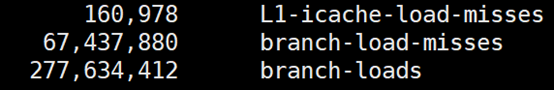

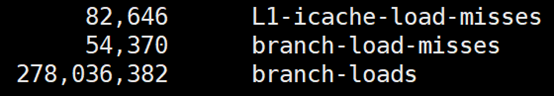

perf工具看来是要找个时间好好看看了。

最早是在linux性能优化专栏看到用到,今天在一篇公众号上看别人用这个快速定位了线上有问题的死循环函数,今天老师又提到了用它看命中率。

工具用好了真的是方便,lsof之前也没用过,后来用了几次觉得非常好用,现在就经常用了。展开作者回复: 我来也同学每篇必有留言被编辑小姐姐选为精品,^_^

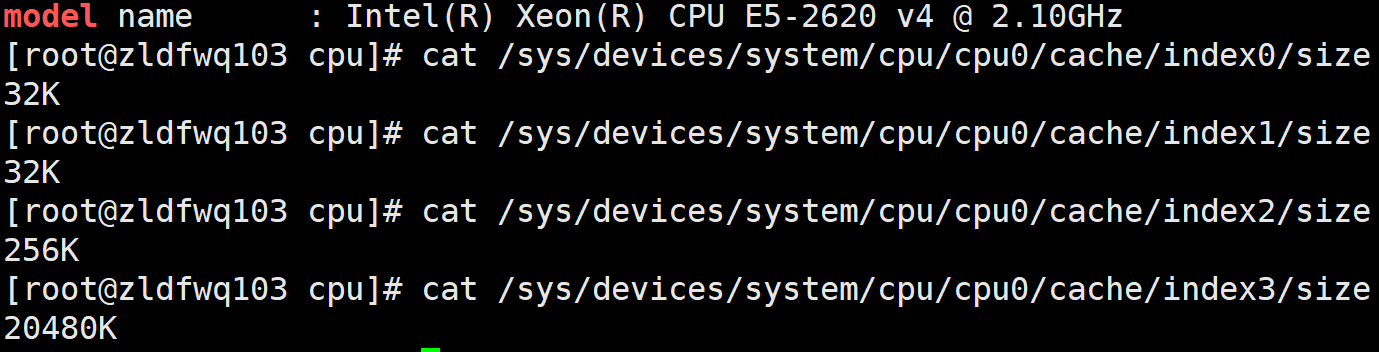

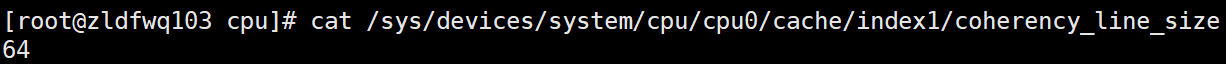

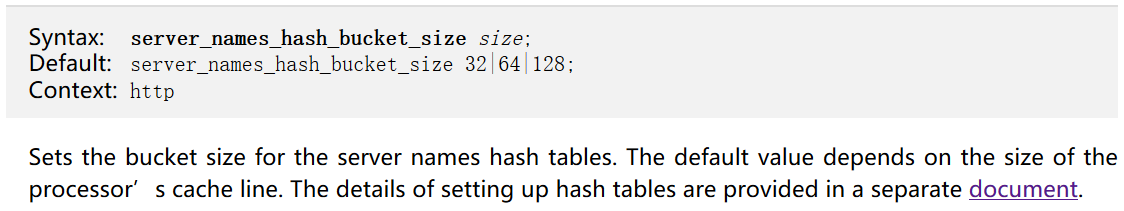

perf没有侵入性,使用简单,效果非常棒,值得你投入精力好好学一学! 1 - 2020-04-28配置 nginx server_names_bucket_siz 的大小

而桶大小为 50 字节,会导致最坏 2 次访问内存,而 70 字节最坏会有 3 次访问内存。

----------------------------------------------------

为什么 50字节会访问2次内存呢? 不是可以加载 64k数据到缓存,包含了 50个字节,一次不就够了吗?

70k 也是同样的问题,为什么是3次啊展开 - 2020-04-28这是因为在多处理器开发中为了保证共享变量的“可见性”。比如声明了volitate的变量,会向处理器发送一条Lock指令。Lock指令会将处理器缓存行中的数据刷回内存,并使其他cpu核心存储了该内存地址的缓存行失效。展开

- 2020-04-28不同线程使用的CPU核心会存在差异,虽然访问的都是同一块连续的变量,但是仅仅只是其中的一个,将后面连续的变量读入缓存没有任何的作用。

另外就算是在同一个cpu上运行的不同线程,访问变量大概率也是有跳跃性的,所以缓存基本就失效了。

不知道理解对不对,请老师指正展开 - 2020-04-28老师,思考题您最后会给一个“官方”的答案吗?展开

作者回复: 你好走马,会的,不过目前二星球的答案已经非常准确啦

- 2020-04-28要学的课程太多了,一入IT深似海。展开

作者回复: 哈哈,不是说,咱们这行业只看能力,学历、专业都不看的,要想保持目前IT行业相对其他行业的高薪资,就得提升入行门槛啊^_^

- 2020-04-28回答完问题,从文章整体的角度又简单理解一下,有些疑惑:

1,关于cpu缓存这块儿老师重点剖析了一级缓存的数据缓存和指令缓存,简单来说呢,数据缓存的大体意思就是尽量访问同一块内存上数据;指令缓存呢就是尽量像cpu的分支预测上面靠。这两个点呢,感觉还是比较薄,要达到这种预期,实际情况下也需要注意一些基础的编程规范。当然可能是我理解的比较浅显哈!请问老师在一级缓存这块儿,还有什么大神级的骚操作吗?毕竟这篇专栏的题目是怎样写代码才……

2,关于cpu二级缓存,三级缓存的优化还会聊到吗?展开 - 2020-04-28这应该是涉及并发编程要解决的可见性问题吧,虽说被缓存了(还是相邻的),但是为了保证可见性的话这种缓存也是不可用的。所以如果要保证并发安全也只能是按需禁用缓存了

- 2020-04-28设置cpu亲和性的时候,如果不同线程处于不同CPU,而又有需要共享的变量,线程切换的时候会造成cache miss,重新加载,性能反而下降。展开 2